Matías Leonetti nació en Olavarría en 1990. Egresó de la Escuela Técnica N° 2 de en el año 2007, y a partir de ese momento comenzó a crear programas de facturación y gestión de stock usando Visual Basic y Access. Comenzó a cursar la carrera de Ingeniería de Sistemas en la Facultad de Ingeniería de Olavarría en 2008, y al año siguiente la continuó en Tandil. Continuó programando y además, para bancar sus estudios, realizó desarrollo y mantenimiento de páginas y hosting web.

Cuando le preguntamos cómo llegó al mundo de Sistemas, nos responde “Siempre me gustó la electrónica (además de sistemas), en especial esa línea difusa entre Hardware y Software, donde el software ya son unos y ceros y son ejecutados por el hardware mediante registros, señales y lógica”. Fue mientras cursó las materias de diseño digital dictadas por el Dr. Elias Todorovich, donde se enseñan HDL (Lenguajes de Descripción de Hardware) y FPGA (Lógica Programable), que se dio cuenta que era su área de especialización. Nos comparte “estos temas me parecieron geniales, además de ser muy exclusivos, ya que no son los más comunes entre los estudiantes”.

En el año 2011, la empresa estadounidense Sonics Inc. especializada en Networks-on-Chip, de la mano de Ray Brinks (Vicepresidente de ingeniería), patrocinó una serie de cursos sobre diseño digital en la Facultad de Ingeniería de Olavarría. En ese momento, no lo pensó dos 2 veces, Matías dio lo mejor de sí y no solo le tomaron los cursos como materias optativas, sino que esa decisión valió la pena y fue así que inició su carrera profesional.

A fin del año 2013, le llegó la oportunidad de realizar un entrenamiento en las oficinas de Sonics en Silicon Valley junto al profesor Todorovich, que luego continuó como pasantía remota por 6 meses. Este trabajo fue presentado como tesis de la carrera y fue publicado en el Instituto de Ingenieros Eléctricos y Electrónicos -IEEE- de Estados Unidos, bajo el título «An Advanced NoC with Debug Services on FPGA (FPGA significa Field-Programmable Gate Array, conocido en español como Lógica Programable), en español “Una Red de Interconexión Avanzada con Servicios de Depuración en Lógica Programable» en 2014. Le siguieron más viajes a sus oficinas y trabajo remoto durante el año 2014.

Se recibió en 2014 y empezó a buscar trabajo en su campo de especialidad y aún teniendo experiencia, no logró conseguirlo en Argentina. Desde chico había soñado con trabajar y vivir en Estados Unidos, entonces comenzó a cargar su CV en las grandes compañías a nivel mundial. La experiencia vivida años antes con los cursos de Silicon Valley sobre los temas de su interés en su ciudad lo había preparado para este momento. En el envío de CVs a empresas internacionales su perfil llegó a Intel en Guadalajara, empresa que lo eligió y le abrió las puertas que estaba buscando y necesitando. Así conoció Estados Unidos, hizo su tesis y continuó por un tiempo de forma remota. Matías sintetiza este momento de su vida de esta manera “Con esa experiencia, me di cuenta donde estaba mi lugar y mi industria en el Mundo.”

En 2015 fue contratado por Intel Corporation en Guadalajara, México, como FPGA Emulation Engineer. Su tarea principal consistía en el prototipado de chipsets, utilizando sistemas multi FPGA como Synopsys HAPS-70, incluyendo automatización, síntesis e implementación. Lideró el modelado del base die del proyecto Lakefield, primera tecnología híbrida de Intel.

En 2018 fue transferido a un nuevo equipo en Folsom, California, donde se desempeña actualmente como System Validation Engineer, validando el componente de seguridad del chipset conocido como Converged Security and Management Engine (Intel CSME). Desarrolla firmware que se utiliza para la validación del hardware de todo el chipset y provee soporte, tanto en el modelado pre-silicio como en la puesta a punto del chip una vez fabricadas las primeras unidades de prueba.

En 2020 alcanzó el rango de Senior Engineer, donde la más reciente tarea fue la validación de la tecnología de detección de ataques conocida como Tunable Replica Circuit (TRC) en el proyecto Alder Lake (Intel 12th Gen), la cual fue publicada tanto internamente como al público en general, y fue presentada en la conferencia internacional de ciberseguridad Black Hack, donde se muestran los últimos avances en cuanto a seguridad contra hackers. Ya que la última validación que hizo es para prevenir la inyección de fallas, le resultó gratificante que sea mostrada a la comunidad. (más sobre esto en este link). También trabajó en la validación del componente de seguridad de tarjetas gráficas Intel Arc, y actualmente se encuentro trabajando en la próxima tecnología de Intel, 14th Gen.

¡Matías es un orgullo de Exactas!

Fotos:

1: Como estudiante, año 2012 (aprox) armando su propia PC

2: Junto a Ray Brinks en las oficinas de Sonics.

3: Junto a Elias Todorovich, usando la FPGA del proyecto en la pasantía en Sonics.

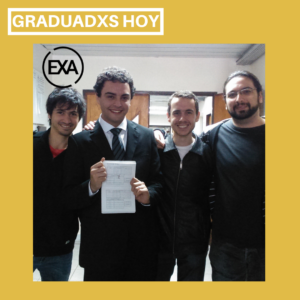

4: Recibida junto a los compañeros de la carrera en 2014.

5: En Guadalajara, mirando a Boca con su esposa. Foto captada por el diario el Popular, año 2017.

6: Una foto hoy: En las afueras de las oficinas de Intel en Estados Unidos.